Coherent/II-VI Foundation Mini-Conference 2025, May 19.

# Unique electron trapping and its impacts on electron mobility in SiC n-channel MOSFETs

X. Chi<sup>1</sup>, K. Ito<sup>1</sup>, T. Suto<sup>2</sup>, A. Shima<sup>2</sup>, K. Mikami<sup>1</sup>, M. Kaneko<sup>1</sup>, T. Kimoto<sup>1</sup>

<sup>1</sup>Kyoto University <sup>2</sup>Hitachi, Ltd. R&D Group

# **Outline of this talk**

- 1. Background and purpose of this study

- 2. Device fabrication and measurements

- 3. Unique carrier trapping near SiC MOS interfaces

- 4. Carrier scattering and physics-based model of SiC MOSFETs

- 5. Summary

# **Outline of this talk**

# 1. Background and purpose of this study

- 2. Device fabrication and measurements

- 3. Unique carrier trapping near SiC MOS interfaces

- 4. Carrier scattering and physics-based model of SiC MOSFETs

- 5. Summary

# **SiC power MOSFETs**

### SiC MOSFETs: next-generation low-loss and high-voltage power devices

SiC MOSFETs in practical use

EV Tesla Model 3

Train

### Remarkable energy saving

https://www.statista.com/chart/16948/total-number-of-premium-cars-sold-in-the-us/ https://jr-central.co.jp/news/release/nws001685.html Research on the highest-performance SiC MOSFET

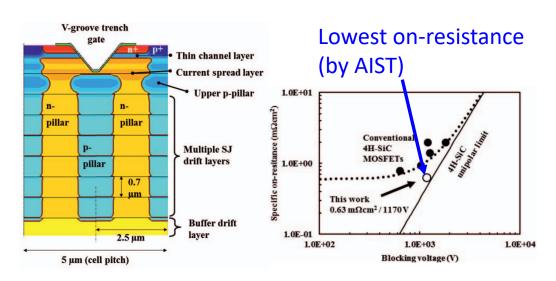

Super Junction V-Groove Trench MOSFET (AIST) [1]  $1170 \text{ V} - 0.63 \text{ m}\Omega\text{cm}^2$

[1] T. Masuda et al., IEDM Tech. Dig. (2018), p. 177.

### The main issue in SiC MOSFETs

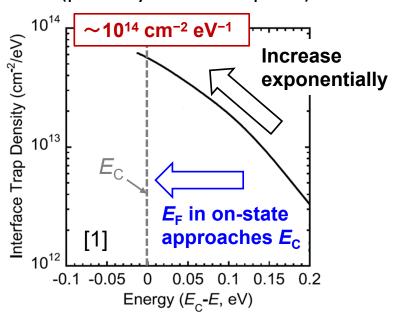

A high density of interface traps exists near the MOS interface (origin is still unclear)

### Energy distribution of interface trap density (Dit)

- D<sub>it</sub>: increase exponentially towards E<sub>C</sub>

- $D_{\rm it}$  near  $E_{\rm C}$ : ~10<sup>14</sup> cm<sup>-2</sup> eV<sup>-1</sup>

- ... 1000 times higher than Si MOS

### Performance degradation caused by high D<sub>it</sub>

$E_{\rm F}$  approaches  $E_{\rm C}$  in the on-state of MOSFETs

Extremely high  $D_{it}$  near  $E_{C}$

- Severe electron trapping

- 2. Coulomb scattering

$\underline{D_{it}}$  distribution near  $\underline{E_C}$  (partially modified quote)

### Main reason for the low channel mobility in SiC MOSFETs

$(\mu_{\rm ch} = 20 \text{ cm}^2/\text{Vs vs.} \, \mu_{\rm bulk} = 1020 \text{ cm}^2/\text{Vs})$

[1] T. Hatakeyama et al., Appl. Phys. Express 12, 021003 (2019).

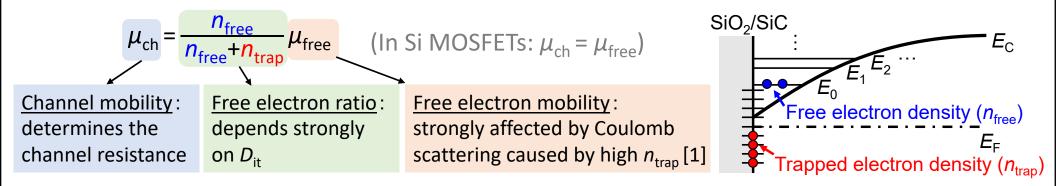

# Impact of interface traps on device characteristics

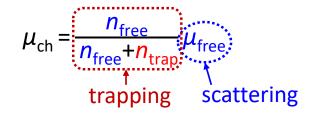

### Relationship of $\mu_{\mathsf{ch}}$ and $\mu_{\mathsf{free}}$ in SiC MOSFETs

$\mu_{ch}$ : include "Trapping" × "Scattering" caused by interface traps

Basic understanding of interface traps: essential for modeling of SiC MOSFETs

However...

There is a lack of comprehensive understanding of interface traps

→ Modeling of SiC MOSFETs is incomplete (a long-standing issue)

[1] K. Ito et al., Appl. Phys. Express 16, 071001 (2023).

# Purpose of this study

To distinguish the impacts of trapping and scattering

$\rightarrow$  Measurements of  $n_{\text{free}}$ ,  $\mu_{\text{free}}$ ,  $n_{\text{trap}}$  are necessary (not  $\mu_{\text{ch}}$ )

### **Previous study**

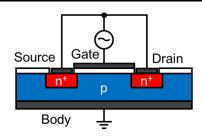

Combine **Split** *C*—*V* and **MOS Hall-effect** measurements [1]

Obtain total electron density  $(n_{total})$

Obtain  $n_{

m free}$  and  $\mu_{

m free}$  separately

$(\mu_{Hall} = \mu_{free})$  with Hall scattering factor = 1)

$n_{\text{trap}} = n_{\text{total}} - n_{\text{free}}$

### Objective

By the measurement and calculation of  $n_{\text{free}}$ ,  $\mu_{\text{free}}$ ,  $n_{\text{trap}}$

- Obtain a comprehensive understanding of the interface traps

- Elucidate electron trapping and scattering mechanisms in SiC MOS channels

Establish a physics-based model for SiC MOSFETs based on a comprehensive understanding of electron trapping and scattering phenomena

[1] T. Hatakeyama et al., Appl. Phys. Express 10, 046601 (2017).

# **Outline of this talk**

1. Background and purpose of this study

### 2. Device fabrication and measurements

- 3. Unique carrier trapping near SiC MOS interfaces

- 4. Carrier scattering and physics-based model of SiC MOSFETs

- 5. Summary

### **Device fabrication and measurements**

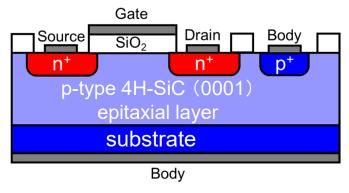

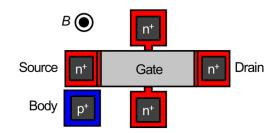

### Device fabrication

### **Gate oxides**

Dry oxidation → NO annealing (standard process) (Oxide thickness: 42 ~ 50 nm)

P-body doping concentrations  $(N_{\underline{A}})$

$7 \times 10^{14}$ ,  $3 \times 10^{15}$ ,  $3 \times 10^{16}$ ,  $3 \times 10^{17}$ ,  $1 \times 10^{18}$  cm<sup>-3</sup>

### Measurements and extraction of $n_{\text{trap}}$

#### Split *C*–*V* measurements

Measurement of  $n_{\text{total}}$

### **MOS-Hall effect measurements**

Measurement of  $n_{\text{free}}$  and  $\mu_{\text{free}}$  (Hall scattering factor = 1)

### Extraction of *n*<sub>trap</sub>

$$n_{\text{trap}} = n_{\text{total}} - n_{\text{free}}$$

# **Outline of this talk**

- 1. Background and purpose of this study

- 2. Device fabrication and measurements

- 3. Unique carrier trapping near SiC MOS interfaces

- 4. Carrier scattering and physics-based model of SiC MOSFETs

- 5. Summary

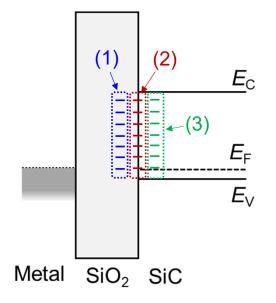

# Possible origins of interface traps

### (1) Near-interface oxide traps (NITs)

- C defects [1]  $(C_0 = C_0^{[2]}, Si_2 C O^{[3]})$

- Intrinsic oxide defects

### (2) Traps at the MOS interface

- C defects (C clusters [1,2], C-C [4])

- Dangling bonds [5]

### (3) Traps in SiC

- Conduction band fluctuations [6, 7]

- C defects ((C<sub>2</sub>)<sub>Si</sub> [8])

### Where are the interface traps primarily located?

### ... Important information for the modeling of SiC MOSFETs

- [1] V. V. Afanasev et al., Phys. Status Solidi A **162**, 321 (1997). [2] P. Deák et al., J. Phys. D: Appl. Phys. **40**, 6242 (2007).

- [3] F. Devynck et al., Phys. Rev. B 84, 235320 (2011).

- [5] T. Umeda et al., Appl. Phys. Lett. 113, 061605 (2018).

- [7] H. Yoshioka et al., AIP Advances 8, 045217 (2018).

- [4] X. Shen et al., Appl. Phys. Lett. 98, 053507 (2011).

- [6] Y. Matsushita et al., Nano Letters 17, 6458 (2017).

- [8] T. Kobayashi and Y. Matsushita, JAP 126, 145302 (2019).

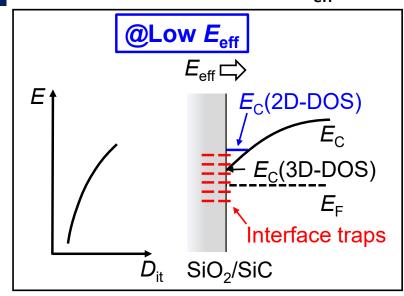

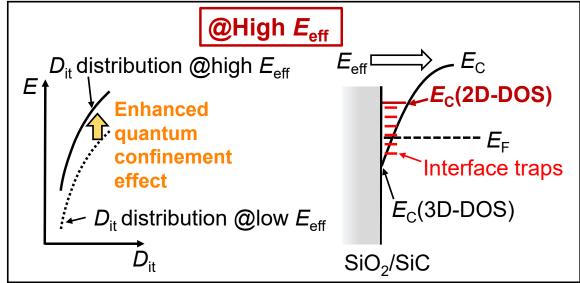

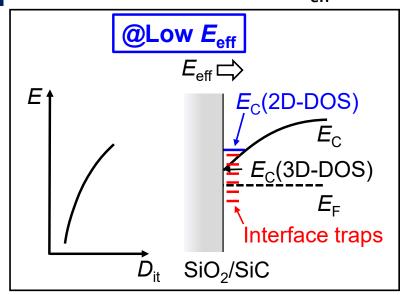

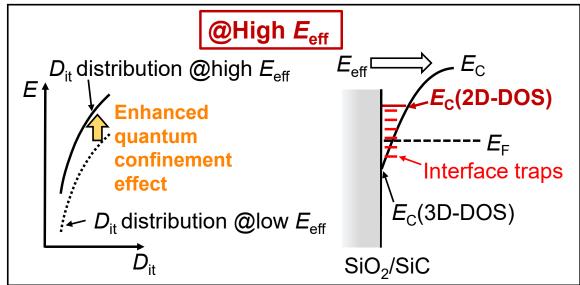

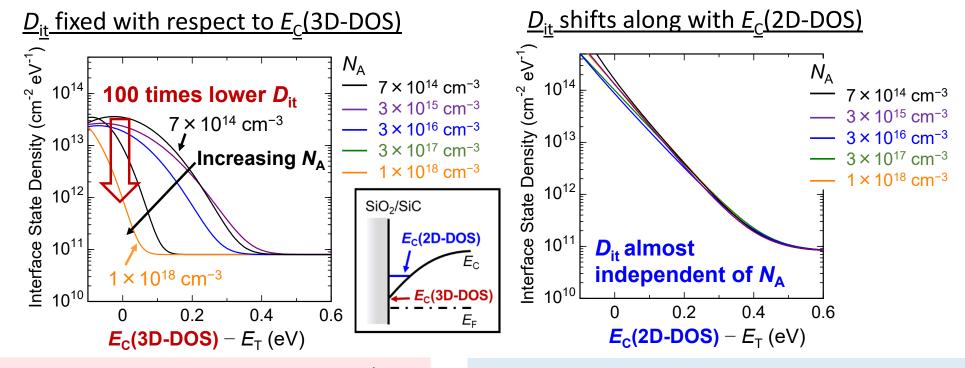

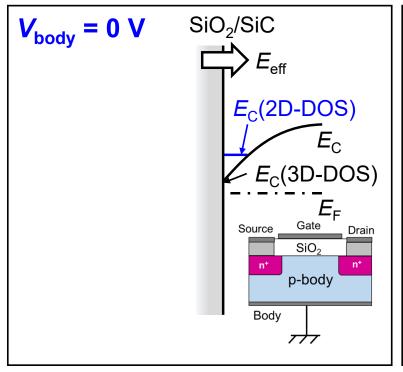

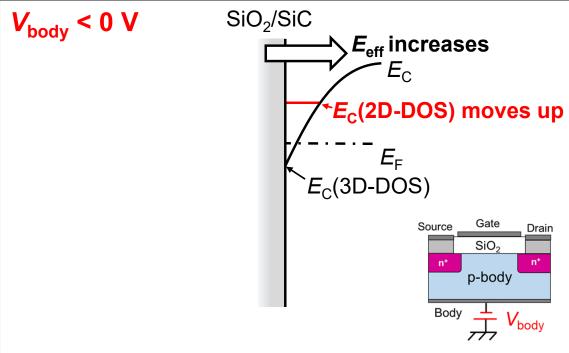

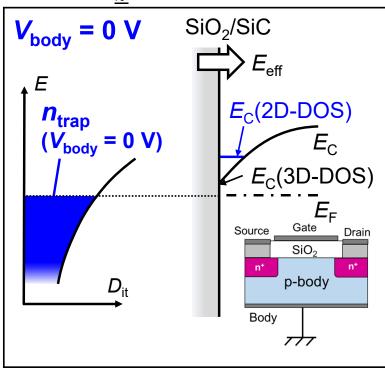

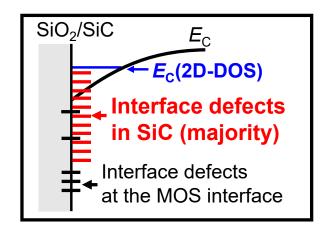

# Quantum confinement effect and D<sub>it</sub> distribution

Increasing effective field  $(E_{eff})$ : enhances the quantum confinement effect

[Case 1] Traps are primarily located within the SiO<sub>2</sub> or at the MOS interface:

$D_{it}$  distribution is energetically fixed with respect to  $E_c$  (3D-DOS)

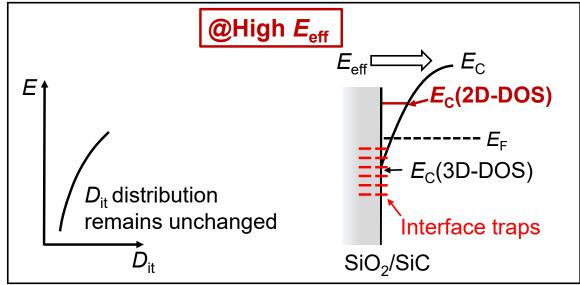

# Quantum confinement effect and D<sub>it</sub> distribution

Increasing effective field  $(E_{eff})$ : enhances the quantum confinement effect

[Case 2] Traps are primarily located in SiC:

$D_{it}$  distribution may shift along with  $E_c$ (2D-DOS)

### Control of E<sub>eff</sub>

$E_{\text{eff}}$  can be controlled by p-body doping concentration ( $N_A$ ) and body bias ( $V_{\text{body}}$ )

$$E_{\text{eff}} = \frac{\sqrt{2e\varepsilon_{\text{SiC}}N_{\text{A}}(2\psi_{\text{B}} - V_{\text{body}}) + en_{\text{free}}/3}}{\varepsilon_{\text{SiC}}}$$

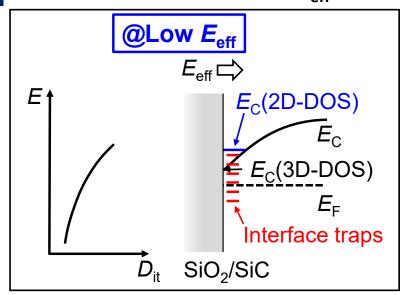

# Quantum confinement effect and D<sub>it</sub> distribution

Increasing effective field  $(E_{eff})$ : enhances the quantum confinement effect

[Case 2] Traps are primarily located in SiC:

$D_{it}$  distribution may shift along with  $E_c$ (2D-DOS)

Clarify where the interface traps are primarily located by investigating whether the  $D_{\rm it}$  distribution shifts along with  $E_{\rm c}$ (2D-DOS) (by changing  $N_{\rm A}$  and  $V_{\rm body}$ )

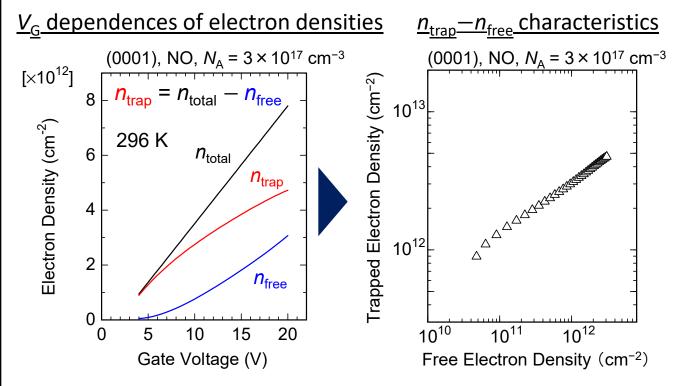

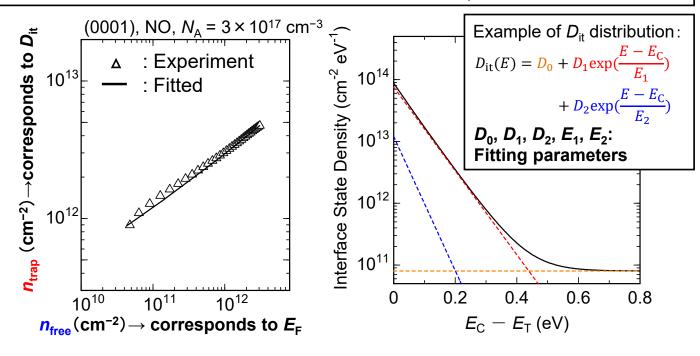

# Experimental results and extraction of D<sub>it</sub> distribution

[1] K. Ito et al., J. Appl. Phys. **128**, 095702 (2020)

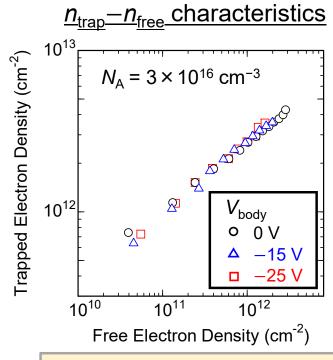

# Experimental results and extraction of Dit distribution

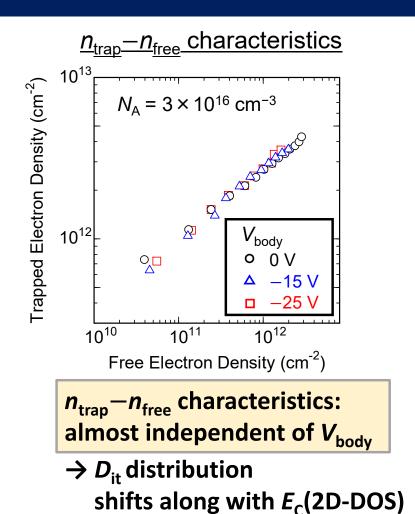

$$n_{\text{trap}} = \int_{E_{\text{i}}}^{\infty} \frac{1}{\exp\left(\frac{E - \boldsymbol{E}_{\text{F}}(\boldsymbol{n}_{\text{free}})}{k_{\text{B}}T}\right) + 1} \boldsymbol{D_{\text{it}}(\boldsymbol{E})} dE$$

#### Extraction method

- 1. Calculate  $E_F$  from  $n_{free}$  self-consistently [1]

- 2. Extract  $D_{it}$  distributions by reproducing  $n_{trap} n_{free}$  characteristics

[1] K. Ito et al., J. Appl. Phys. **128**, 095702 (2020)

# Experimental results and extraction of D<sub>it</sub> distribution

$$n_{\text{trap}} = \int_{E_{\text{i}}}^{\infty} \frac{1}{\exp\left(\frac{E - \boldsymbol{E}_{\text{F}}(\boldsymbol{n}_{\text{free}})}{k_{\text{B}}T}\right) + 1} \boldsymbol{D_{\text{it}}(\boldsymbol{E})} dE$$

#### Extraction method

- 1. Calculate  $E_F$  from  $n_{free}$  self-consistently [1]

- 2. Extract  $D_{it}$  distributions by reproducing  $n_{trap} n_{free}$  characteristics

Calculate for cases where the  $D_{it}$  distribution is energetically fixed with respect to  $E_c(3D-DOS)/shifts$  along with  $E_c(2D-DOS)$

[1] K. Ito et al., J. Appl. Phys. **128**, 095702 (2020)

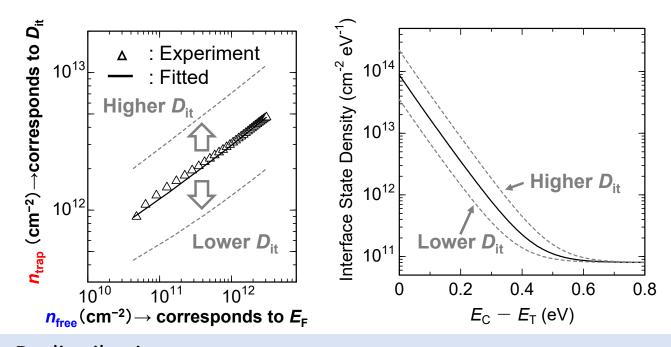

# $D_{it}$ distributions extracted from $n_{trap} - n_{free}$ characteristics

$D_{\rm it}$  values sharply decrease with  $N_{\rm A} \uparrow$  ... Hardly understandable

$D_{it}$  almost independent of  $N_A$  (determined by process) ... Reasonable result

$D_{it}$  distribution depends on  $N_A$ ? ... Need to verify using the same device

$\rightarrow$  Focus on the **body bias effect**

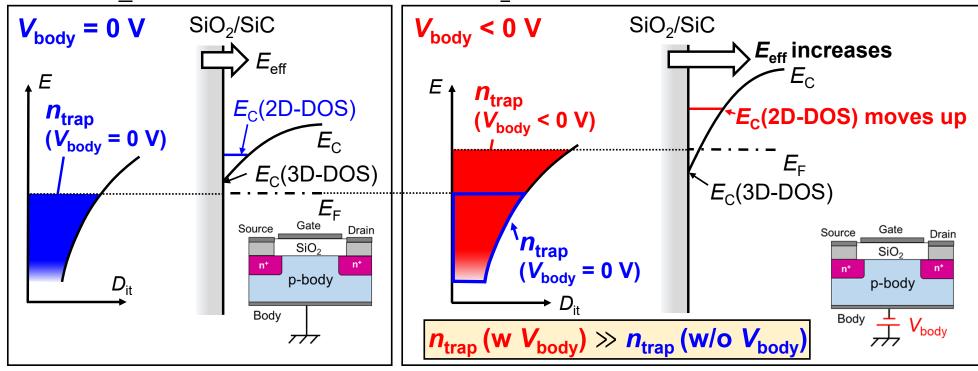

# Impact of body bias on $n_{\text{trap}}$

# Negative body bias $(V_{body})$ : increases $E_{eff}$

# Impact of body bias on $n_{\text{trap}}$

Compare  $n_{\text{trap}}$  for the cases where  $V_{\text{body}} = 0 \text{ V}$  and  $V_{\text{body}} < 0 \text{ V}$  (@a given  $n_{\text{free}}$ )

[Case 1]  $D_{it}$  distribution fixed with respect to  $E_{c}$ (3D-DOS)

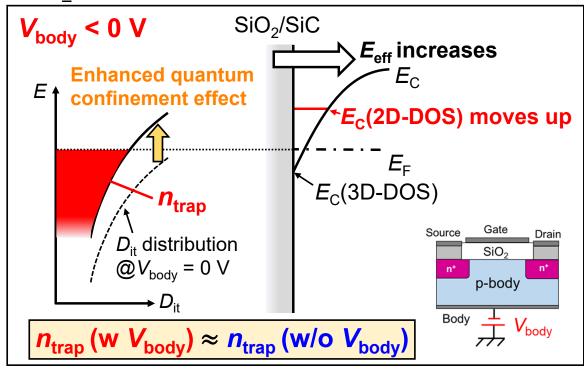

# Impact of body bias on $n_{\text{trap}}$

Compare  $n_{\text{trap}}$  for the cases where  $V_{\text{body}} = 0 \text{ V}$  and  $V_{\text{body}} < 0 \text{ V}$  (@a given  $n_{\text{free}}$ )

[Case 2]  $D_{it}$  distribution shifts along with  $E_{C}$  (2D-DOS)

It is possible to verify whether the  $D_{it}$  distribution shifts along with  $E_{C}(2D-DOS)$

by comparing  $n_{\text{trap}}$  under various  $V_{\text{body}}$

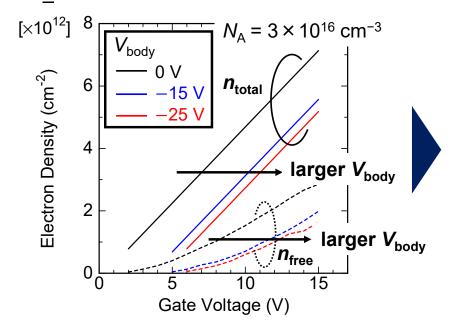

# **Body bias measurement results**

### V<sub>G</sub> dependences of electron densities

Positive shifts according to  $V_{\rm body}$

$\rightarrow$  Appropriate control of  $V_{\text{body}}$

$n_{\text{trap}} - n_{\text{free}}$  characteristics: almost independent of  $V_{\text{body}}$

$\rightarrow D_{it}$  distribution shifts along with  $E_c$ (2D-DOS)

# **Body bias measurement results**

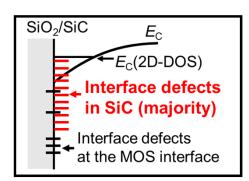

# **Electron trapping inside SiC**

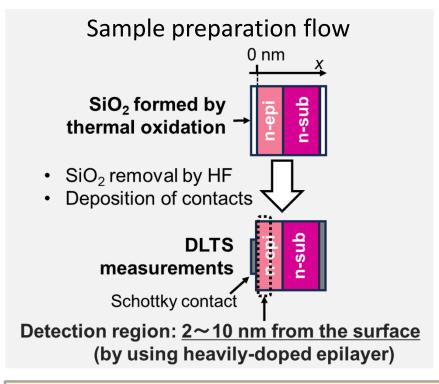

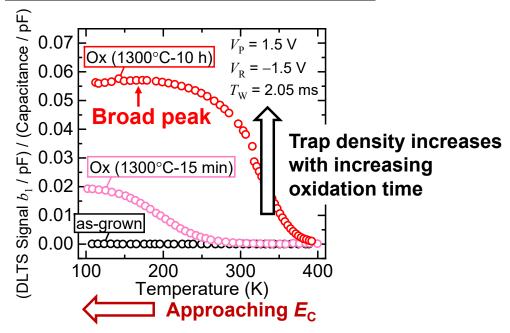

### Thermal oxidation of SiC: generates multiple defect levels near $E_{c}$ [1]

### **DLTS** spectra of fabricated samples

Defects inside SiC induced by oxidation: a primary origin of interface traps ... Electrons are trapped mainly inside SiC

[1] H. Fujii et al., Appl. Phys. Express 17, 041004 (2024).

# **Outline of this talk**

- 1. Background and purpose of this study

- 2. Device fabrication and measurements

- 3. Unique carrier trapping near SiC MOS interfaces

- 4. Carrier scattering and physics-based model of SiC MOSFETs

- 5. Summary

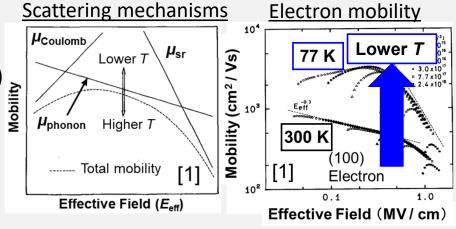

# **Electron scattering mechanism in MOS channels**

### In Si MOSFETs (extremely low $D_{it}$ )

- Dominant scattering mechanism  $[\bot]$  @Low- $E_{eff}$ : Coulomb scattering (ionized impurities)

- @High- $E_{eff}$ : Surface roughness (sr) scattering

- With lowering the temperature...

$\mu_{\mathsf{Coulomb}}$  : decreases

$\mu_{\text{phonon}}$ : increases

[1] S. Takagi et al., IEEE Trans. Electron Devices **41**, 2357 (1994).

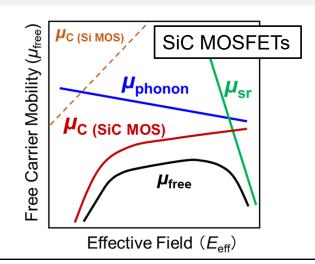

### In SiC MOSFETs

High density of interface defects near the MOS interface

Coulomb scattering by non-ideal charges is dominant [2, 3] (trapped electrons and fixed charges)

### Extremely difficult to distinguish $\mu_{ exttt{phonon}}$ and $\mu_{ exttt{sr}}$

[2] M. Noguchi et al., Jpn. J. Appl. Phys. 59, 051006 (2020).

[3] K. Ito et al., Appl. Phys. Express 17, 081003 (2024).

# Previous report and our approach

### Previous report on scattering mechanism in SiC MOS channels [1]

Measurements of  $\mu_{\text{free}}$  in MOSFETs with various  $N_{\text{A}}$

- In lightly-doped MOSFETs:  $\mu_{\text{free}} \approx \mu_{\text{phonon}}$

- Extraction of  $\mu_{\rm phonon}$ ,  $\mu_{\rm sr}$ , and  $\mu_{\rm Coulomb}$  based on empirical rules

- ... Still lack of a physical understanding of electron scattering mechanism

[1] M. Noguchi et al., IEDM Tech. Dig. (2017), p. 219.

### Our approach

- Measure  $\mu_{\text{free}}$  with varying  $N_{\text{A}}$  and temperature systematically

- Perform numerical calculation of  $\mu_{\text{free}}$  (considering the electron trapping inside SiC) New in this study

- Discuss the scattering mechanism

by comparing the calculated and experimental results

# Calculation method of inversion layer mobility

### **Electronic states**

Self-consistent loop

Schrödinger equation

- Subband energies

- Wavefunctions

Poisson equation

Potential distribution

### **Momentum relaxation time**

(next slide)

### **Free electron mobility**

Calculated under the relaxation time approximation

[1] H. Fujii et al., Appl. Phys. Express 17, 041004 (2024).

# Calculation method of inversion layer mobility

### **Electronic states**

Self-consistent loop . Schrödinger equation

- Subband energies

- Wavefunctions

**Poisson equation**

Potential distribution

Momentum relaxation time (next slide)

### **Free electron mobility**

Calculated under the relaxation time approximation The electron trapping inside SiC

Calculate  $n_{\text{trap}}$  with  $D_{\text{it}}$  distribution

$n_{\text{trap}} = \int_{E_i}^{\infty} f(E) \, D_{it}(E) dE \quad D_{it}(E)$ : shifts along with  $E_{\underline{C}}(2D-DOS)$

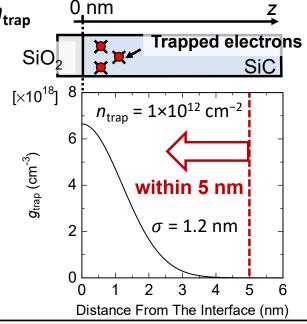

Calculate the distribution of  $n_{\text{trap}}$

Depth profile of  $n_{\text{trap}}$ :

$$g_{\text{trap}}(z) = \frac{2n_{\text{trap}}}{\sqrt{2\pi\sigma^2}} \exp(-\frac{z^2}{2\sigma^2})$$

(half Gaussian function [1])

Trapped electrons:

Distributed within 5 nm

from the MOS interface

[1] H. Fujii et al., Appl. Phys. Express 17, 041004 (2024).

Common to

Si MOS

# **Scattering mechanism**

### Phonon scattering

- Acoustic phonon (ac) & Non-polar optical phonon (nop) scatterings [1]

- Parameters: deformation potential  $(D_{ac}, D_{nop})$ (Adjusted from the bulk deformation potentials  $D_{ac, bulk}$  and  $D_{nop, bulk}$  [2])

### Surface roughness (sr) scattering

- Correlation function:  $\langle \Delta(r_0)\Delta(r_0+r)\rangle = \Delta_{\rm Sr}^2 {\rm e}^{-\sqrt{2}|r|/L_{\rm Sr}}$  (common to Si MOS) [1]

- Parameters: height  $(\Delta_{sr})$  and correlation length  $(L_{sr})$  of surface roughness

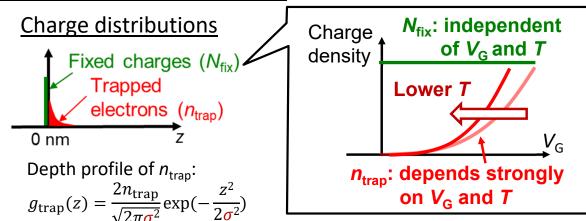

### **Coulomb scattering by non-ideal charges (peculiar to SiC MOS)**

Fixed charges  $(N_{fix})$

- Locates at the MOS interface

- N<sub>fix</sub> value: fitting parameter

Trapped electrons  $(n_{trap})$

- $n_{\text{trap}}$ : calculated with  $D_{\text{it}}$  distribution

- Distributes inside SiC

( $\sigma$ : fitting parameter)

[1] H. Tanaka and N. Mori, Jpn. J. Appl. Phys. **59**, 031006 (2020). [2] H. Iwata and K. M. Itoh, J. Appl. Phys. **89**, 6228 (2001).

# **Scattering mechanism**

#### Phonon scattering

- Acoustic phone

- Parameters: de

### Surface roughne

- Correlation fur

- Parameters: he

#### **Coulomb scatter**

Fixed charges (N<sub>f</sub>

- Locates at the

- N<sub>fix</sub> value: fitti

Trapped electron

- n<sub>trap</sub>: calculate

- Distributes ins

(σ: fitting par

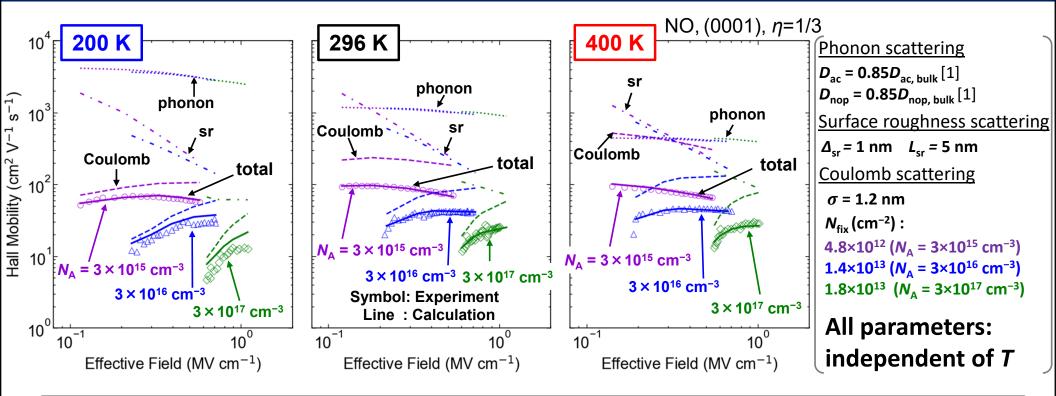

Parameters are uniquely determined by simultaneously reproducing experimental  $\mu_{\rm Hall}$  at different temperatures

Common to Si MOS

er T

ver T

ver T

ver Sends strongly

V<sub>G</sub> and T

[1] H. Tanaka and N. Mori, Jpn. J. Appl. Phys. **59**, 031006 (2020). [2] H. Iwata and K. M. Itoh, J. Appl. Phys. **89**, 6228 (2001).

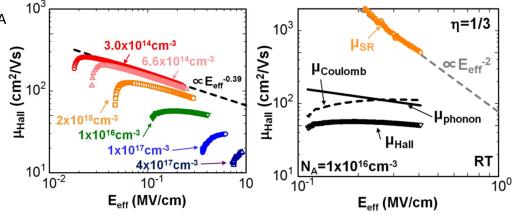

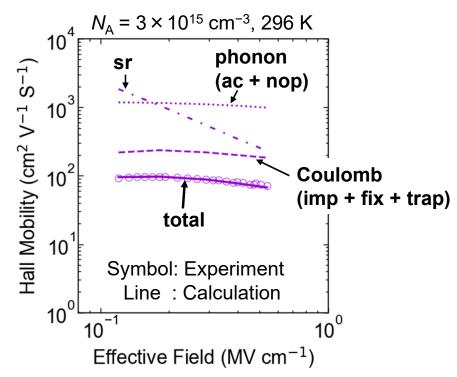

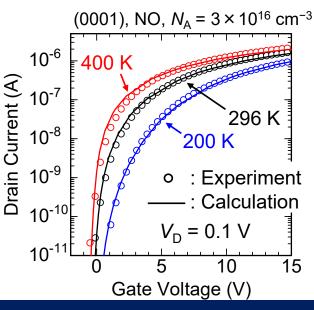

# Experimental and calculated $\mu_{\text{free}}$

Reproducing experimental  $\mu_{Hall}$  in a wide range of  $E_{eff}$  and T with reasonable parameters

→ Elucidation of the electron scattering mechanism in SiC MOS channels

[1] H. Iwata and K. M. Itoh, J. Appl. Phys. 89, 6228 (2001).

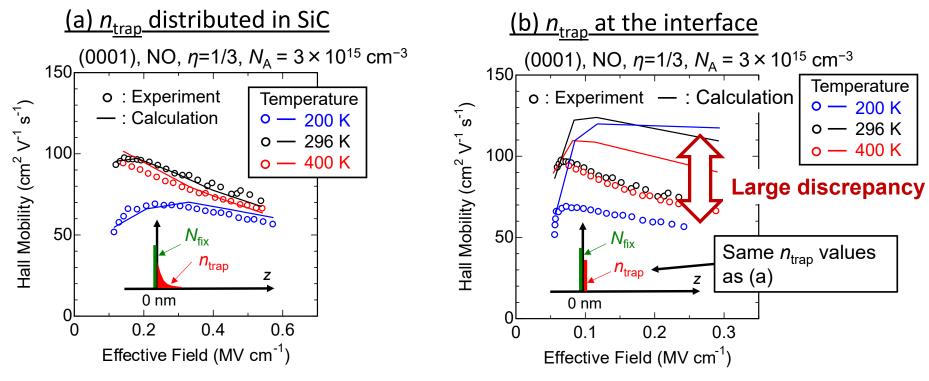

# Validation of electron trapping inside SiC

Calculations consider trapped electrons only at the MOS interface were also performed

Calculated results for case (b): much different from the experimental results

→ Trapped electrons are actually distributed inside SiC

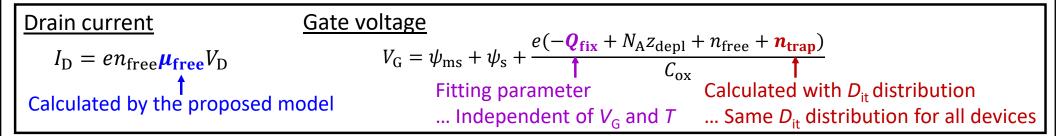

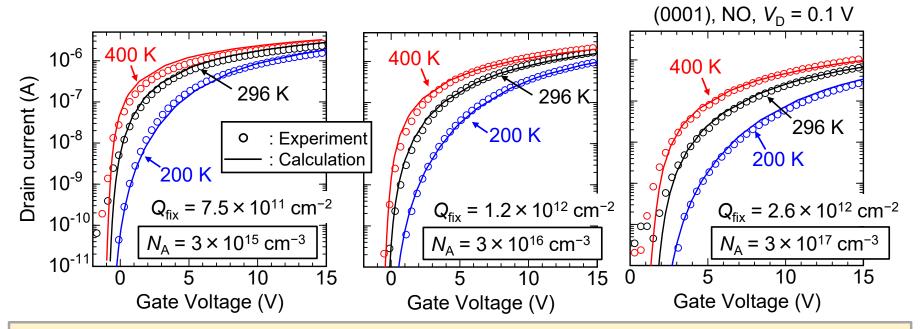

# **Calculation of gate characteristics**

Good agreement with experimental results in a wide  $I_D$  range from  $10^{-10}$  to  $10^{-6}$  A

# **Outline of this talk**

- 1. Background and purpose of this study

- 2. Device fabrication and measurements

- 3. Unique carrier trapping near SiC MOS interfaces

- 4. Carrier scattering and physics-based model of SiC MOSFETs

### 5. Summary

# **Summary**

Modeling of SiC MOSFETs based on a physical understanding of electron trapping and scattering mechanisms in SiC MOS channels

- ☐ Unique carrier trapping near SiC MOS interfaces

- $D_{it}$  distribution in SiC MOS shifts along with  $E_{c}$ (2D-DOS)

- → Most of the interface traps are located inside SiC (Electrons are trapped mainly inside SiC)

- ☐ Carrier scattering and physics-based model of SiC MOSFETs

- Calculations that take into account the electron trapping inside SiC

- $\rightarrow$  Successfully reproduced  $\mu_{\rm Hall}$  and gate characteristics in the temperature range of 200  $\sim$  400 K

First physics-based model for SiC MOSFETs

# **Self Introduction**

### Xilun Chi

Kyoto University, Dept. of Electronic Sci. & Eng.

- **Degree**: third-year Ph.D. student

- Undergraduate Studies: Electrical and Electronic Engineering

- Research Topic: Carrier Scattering and Mobility Modeling in SiC MOS Channels

- <u>Awards</u>: IEEE EDS Japan Joint Chapter Student Award (Feb. 2025)

- <u>Publications</u>: 2 papers (IEDM Tech. Digest, JJAP)

- Presentations: 3 times at ICSCRM (2 oral, 1 poster),

1 time at IEDM (oral)